北京大学集成电路学院在芯片设计自动化EDA领域取得进展

2024/03/28

|

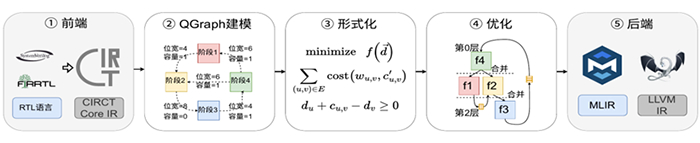

图 Khronos芯片仿真架构

在国家自然科学基金项目(批准号:T2293700、T2293701)等资助下,北京大学集成电路学院黄如院士与梁云教授团队近期提出了高效的芯片仿真EDA技术。针对通用处理器、密码学、流式压缩、深度学习等多种架构的芯片设计,相比于目前最快的开源芯片仿真器Verilator,该技术能够将芯片仿真速度平均加速2倍,最高加速4.3倍。论文以《Khronos:融合内存访问的RTL仿真》(Khronos: Fusing Memory Access for Improved RTL Simulation)为标题,于2023年10月28日发表在《芯片微架构国际研讨会》(International Symposium on Microarchitecture,简称MICRO)上。论文链接:https://doi.org/10.1145/3613424.3614301。

芯片仿真是芯片设计与验证中不可或缺的一个环节,同时也是最耗时的一个环节。芯片仿真主要借助EDA工具,通过计算机结合测试激励来模拟芯片在真实环境下的运行状况,帮助工程师通过各种调试手段来判断运行结果是否符合预期。根据统计,芯片设计与验证的70%的时间用在仿真和验证。芯片仿真中的一个重要步骤是寄存器传输级(RTL)仿真。在RTL仿真中,软件RTL仿真器因为其灵活性高和调试能力强,在RTL仿真中有重要的地位。然而,软件RTL仿真速度慢,需要消耗大量时间。广泛使用的软件RTL仿真器主要来自美国的EDA公司包括新思(Synopsys)的VCS,英特尔(Intel)的ModelSim和开源的Verilator等。针对工业级的大规模设计,软件RTL仿真往往需要几天甚至几周的时间,严重制约了芯片开发的流程。因此,面对芯片开发时间长的问题,加快RTL仿真的速度非常重要。

针对这一难题,该研究团队开创性地提出了跨时钟周期的RTL仿真方法,能够大幅减小RTL仿真迭代中的内存数据传输。之前针对RTL仿真的加速主要是通过图分割并行或延迟求值(lazy evaluation)等方法。虽然这些优化方法在加速仿真上有效,但优化能力局限在了一个周期内。该研究团队通过分析RTL的时钟边缘数据依赖,将RTL仿真建模为整数线性约束下的非线性优化问题,通过数学建模和求解实现跨周期的仿真优化与加速。这样的优化能显著提升仿真过程中的指令吞吐量,减小仿真需要的指令总数。通过跨时钟优化,减少42%的寄存器状态和38%的内存访问,实现平均2.0倍(最高4.3倍)的仿真加速。

目前,该仿真器已经开源,开源链接:https://github.com/pku-liang/ksim。接下来,团队将继续优化性能,同时将技术推广到中国的EDA产业和开源社区。

文章来源国家自然科学基金委员会,分享只为学术交流,如涉及侵权问题请联系我们,我们将及时修改或删除。

-

2025年智能光子学与应用技术国际学 06-10

-

2025年8月优质学术会议推荐 589

-

2025年第十二届能源与环境研究国际 400

-

2025年机械工程,新能源与电气技术 559

-

2025年计算机科学、图像分析与信号 553

-

2025年材料化学与燃料电池技术国际 493

-

第七届精神病学国际大会(CP 202 08-01

-

第七届老龄化与老年医学国际学术会议( 08-01

-

第十四届心理学与健康国际学术研讨会( 08-01

-

第七届测绘与地理信息国际研讨会(CS 08-01

-

第七届大气与海洋科学国际研讨会(SA 08-01

-

第十一届地质灾害研究与防治国际学术会 08-01

-

第十六届地质和地球物理学国际会议(I 08-01

-

第七届细胞科学与再生医学国际研讨会( 08-01

-

第七届合成生物学与生物医学国际研讨会 08-01

-

2025最新JCR分区及影响因子1939

-

好学术:科研网址导航|学术头条分468

-

《时代技术》投稿全攻略:一位审稿499

-

2025年国际期刊预警名单发布!600

-

2025年中科院期刊分区表重磅发3957

-

中科院已正式发布2024年预警期861

-

2025年度国家自然科学基金项目727

-

中国科协《重要学术会议目录(202733

-

2024年国家自然科学基金项目评1138

-

2024年JCR影响因子正式发布1214

-

吉林大学校长张希:学术会议中的提1391

-

SCI论文插图全攻略:从规范解析08-01

-

国际学术会议参加经验是怎么样的呢08-01

-

掠夺性会议是怎么进行判断的呢?—08-01

-

SCI论文投稿费怎么交?202408-01

-

上海易标科技 18269

-

第六届中国果菜产业发展论坛组委会 17922

-

华南出版社(广东)有限公司 7885

-

上海意凡森医药科技发展有限公司 24011

-

AIEC学术交流资讯中心 24212

-

中国化工学会培训中心 2039

-

IAASE 22950

-

fdafe 24032

-

林奇钢管有限公司 20955

-

江苏满程千渠会展服务有限公司 8803

-

北京伊诺永明公关策划有限公司 22986

-

中国电池工业网 21068

-

清华大学生命科学学院 21105

-

首都医科大学 21170

-

上海微纵文化传播有限公司 8015

-

兰州理工大学能源与动力工程学院 20991

-

Terrapinn Singap 20991

-

WILL 8157

-

云南农业大学水利水电与建筑学院 21019

-

上海同济大学 20922

687

687